VIVADO 에서 input timing constraint를 주려고 보면 예전 ISE등을 사용하던 사람한테는 좀 낯설다.

이것에 대해서 아래의 그림을 참고하여 XDC에 적용하여 넣어 주자.

먼저 System Sync.다

System Sync.는 외부 Clock을 기준으로 Data를 입력 받는 경우를 말한다.

즉, 타이밍적으로는 같은 Clock인데, Clock 을 입력받는 곳과 Data를 입력 받는 곳이 다른 경우 이다.

1. System Sync. SDR Rising Edge 를 기준으로 줄 경우

처음 이 그림을 보면 뭔가 예를 잘못 들은 것 같은 느낌 일 것이다.

이 그림에서 의미하는 타이밍은 위의 노란색 F/F 이 아니라

위의 F/F 으로 데이터를 보내는 전단의 F/F의 Clock to Q를 Delay를 의미 한다.

2. System Sync. SDR Falling Edge 를 기준으로 줄 경우

3. System Sync. DDR Edge 를 기준으로 줄 경우

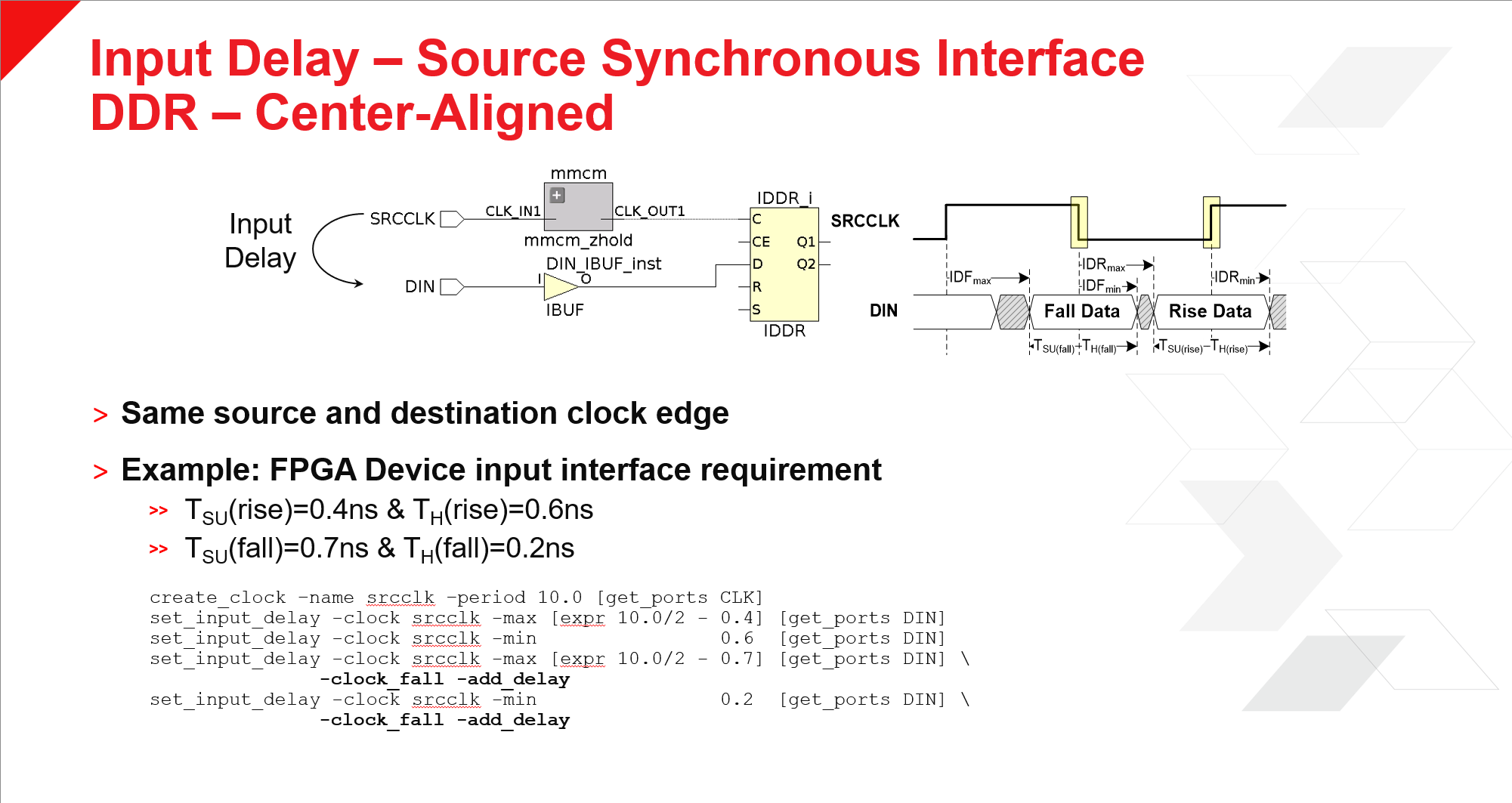

다음은 Source Sync. 기준이다.

Source Sync.는 보내는 측에서 Clock 과 Data를 함께 보낼 경우를 말한다.

4. Source DDR Edge

5. Source DDR Centor

6. Source SDR Rising

7. 6. Source SDR Falling

'Xilinx FPGA' 카테고리의 다른 글

| PCIe IP 생성 (0) | 2020.12.07 |

|---|---|

| VIVADO 에서 Digilent Cable을 2개 이상 연결시 FPGA down load (0) | 2020.09.23 |

| VIVADO XDC Timing Clock Async. 지정 (0) | 2020.09.18 |

| Kintex UltraScale IODELAY (0) | 2020.09.08 |

| Kintex UltraScale 에서 SERDES 사용시 고려사항 (0) | 2020.09.02 |